3DIC将不同工艺制程、不同性子的芯片以三维堆叠的办法整合在一个封装体内,供应性能、功耗、面积和本钱的上风,能够为#5G#、HPC、#AI技能#、#汽车电子#等领先运用供应更高水平的集成、更高性能的打算和更多的内存访问。

然而,3DIC作为一个新的领域,之前并没有成熟的设计剖析办理方案,利用传统的脱节的点工具和流程对设计收敛会带来巨大的寻衅,而对旗子暗记、电源完全性剖析的需求也随着垂直堆叠的芯片设计盛行而爆发式增长。

#芯和半导体#3DIC前辈封装设计剖析全流程EDA平台是一个由芯和半导体完备主导的平台。

凑集了3DIC Compiler 业界顶级的面向2.5D/3D多裸晶芯片系统设计和剖析能力和芯和Metis在2.5D/3D前辈封装领域的强大仿真剖析能力;

由芯和海内团队卖力售前和售后的支持与做事,供应无时差的快速相应和技能反馈;

全面支持#台积电#和#三星#的前辈封装工艺节点。

视频加载中...

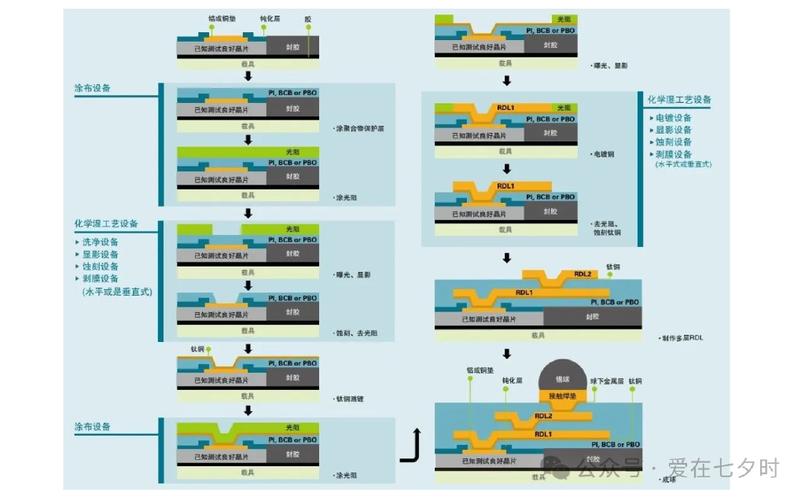

该平台供应了从架构探索、物理实现、剖析验证、旗子暗记完全性仿真、电源完全性仿真到终极签核的3DIC全流程办理方案,是一个完备集成的单一操作环境,极大地提高3DIC设计的选代速率,并做到了全流程无盲区的设计剖析自动化。

通过创始“速率-平衡-精度”三种仿真模式,帮助工程师在3DIC设计的每一个阶段,根据自己的运用处景选择最佳的模式,以实现仿真速率和精度的权衡,更快地收敛到最佳方案,芯和3DIC前辈封装设计剖析全流程#eda#平台能同时支持芯片间几十万根数据通道的互连,具备了在芯片-Interposer-封装全体系统级别的协同仿真剖析能力。

3DIC前辈封装设计剖析流程图

紧张上风1.统一的设计环境

工业界唯一的3DIC设计、剖析、验证全流程办理方案

2.精彩的可拓展性

在上千亿数量级的晶体管上实现片上系统集成

3.超高的设计效率

用前辈的实现和剖析引擎加快探索和设计

4.金牌级的签核

全范围的设计闭合和收敛到优化的PPA/mm3

5.顶尖的多物理场剖析能力

集成业界顶尖的旗子暗记、电源完全性以及热剖析平台,实现快速的收敛并减少设计迭代

3DIC Compiler业内仅有的统一、2.5D和3D多裸晶芯片封装协同设计与剖析

产品总览

3DIC Compiler 平台是一个完全的端到端办理方案,用于高效的2.5D和3D多裸晶系统集成。3DIC Compiler 建立在Fusion Design Platform的通用的、统一数据模型的根本架构之上,并结合了浩瀚变革性的多裸晶设计功能,以供应一个从架构到签核的完全的平台。而所有这些都在一个独特的、整合的用户环境中。这种超领悟的办理方案集成了:沉浸式2D和3D可视化功能、跨层探索和方案、设计和实现、DFX 以及系统级验证和签核剖析,以带来超高水平的设计效率,以及扩展容量和性能的能力,从而无缝支持多个堆叠的异构工艺裸晶,包括数十亿个裸晶间连接。

主要特色

1.高度可扩展的数据环境可以实现数千亿晶体管的2.5D/3D芯片系统集成

2.创新直不雅观的2D、3D界面可以加快设计、仿真、验证的韶光周期

3.集成业界前辈的STA/SI/PI/Thermal等剖析平台,可实现快速设计收敛与最佳的PPA/mm3

4.支持主流Foundry的工艺文件格式与常用封装文件格式

5.基于GUI的设计界面,可以支持数亿Bump与TSV的自动化管理与方案

6.支持丰富多样的3DIC版图互联

Auto-HBM Routing,RDL Routing,Custom Routing,PG Routing,Signal Routing,Bus/Trunk Routing

7.支持快速自动化的基于InFO工艺的繁芜Fan out版图设计

8.支持快速自动化的基于CoWoS的版图互连,PG Mesh天生,MiM&iCap插入,全芯片验证等

Metis-2.5D/3DIC前辈封装剖析产品总览

芯和半导体的Metis是一款运用于裸芯片、3DIC、Chiplet或者前辈封装联合仿真的EDA仿真平台,可以与3DIC Compiler设计环境无缝集成,形成业界独一无二的3DIC设计、仿真、验证办理方案。它许可用户跳过传统建模工具的繁琐配置,并通过考虑关键区域的全体物理环境来快速精准地实现仿真设计的优化;Metis内嵌的三维全波高精度电磁仿真引擎MoM Solver可以涵盖DC-THz的仿真频率,完备知足异构集成中高速高频等运用的精度哀求,并可以完美支持纳米到厘米级别的跨尺度仿真;同时集成芯和独创的Absorbing Fence,Magnetic Current和Mesh Tunneling等核心技能,可以在担保精度的条件下,实现超大规模异构封装的仿真需求。

主要特色

1.Metis集成的跨尺度打算引擎可以完美支持芯片-封装-板级协同仿真剖析

2.支持多核/多机并行打算技能(XHPC),可以大幅度提高仿真剖析效率

利用矩量法ACA算法压缩之后矩阵块的低秩属性来实现多机内存级别分布式打算、打破求解规模限定创始矩阵级分布式求解器,许可访问无限的打算能力和内存(Azure,AWS)。

3.支持仿真求解TSV侧壁上的耗尽层(SiO2)

与同类工具比较,Metis处理SiO2的方法能担保设计性能无损。

4.互连模型提取

Metis可以利用一个单一的求解器为HBM和芯片封装TSV通道提取互连模型,避免涌现切割和缝合的缺点。支持导入GDS和ODB++文件格式。5.Interposer布线建模

HBM旗子暗记在ASIC芯片和HBM内存颗粒之间传输。Metis许可用户通过引导实现interposer建模,帮助用户准确仿照不同芯片掷箭的通道损耗和串扰。

6.TSV建模

由于TSV引入的损耗和串扰,具有TSV的芯片-封装通道对通道性能至关主要。Metis可以准确地提取芯片-封装通道的模型。

7.封装/基板建模

为了实现对付系统SI和PI性能的评估,封装基板上的传输线和配电网络须要精确的EM仿真。Metis为FCBGA封装供应了方便的仿真引导。

8.通道仿真

ChannelExpert供应了一种利用Metis提取的互连模型构建通道的快速方法。通过运行通道仿真,设计职员可以根据内置合规性规范检讨性能,并在必要时优化通道。

文章来源:3DIC前辈封装设计剖析全流程EDA平台是什么? - 知乎

芯和半导体Xpeedic官网(Xpeedic)供应丰富技能资料、设计视频、产品手册等资源,涵盖产品、运用及行业的多种办理方案。欢迎前往官网理解更多详情。

更多EDA前沿趋势、展会信息,可前往芯和半导体微信公众年夜众号:Xpeedic