接口名称:MIPI

英文全称:Mobile Industry Processor Interface

中文:移动工业处理器接口

标准掩护:MIPI同盟/MIPI Alliance(2003年景立)

当前规范:www.mipi.org

紧张内容:分为MIPI M-PHY、D-PHY及C-PHY。M-PHY是Gear 1速率可达1000MHz的物理层。

MIPI同盟的胃口很大,其标准险些把所有与移动设备有关的接口都包含了,以是全体MIPI标准接口是一个系列标准,包括Audio、Camera&Imaging、Chip-to-chip/IPC、Control&Data、Debug&Trace、Display&Touch、Physical Layers and Software Integration ,etc.感兴趣的可以访问其主页mipi.org理解详情。当然,完全的理解与学习这些标准与规范须要很多韶光。这里紧张摘录一些常用的接口规范,例如物理层、显示DSI&DSI-2、摄像头掌握CSI-2&CSI-3、I3C、REFE、UniPro和Soundwire(or Soundwire I3S)等等。

关于物理层Physical Layer当前版本有:

M-PHY (v4.1, Mar.2017) --差分物理层,紧张为UFS接口运用设立。C-PHY (v2.0, Sep.2019) 对应于 CSI-2和DSI-2D-PHY (v2.5, Oct. 2019) 对应于CSI-2和DSI-2A-PHY ---针对Automotive(即将推出 )解释:它是一种数字化视频/音频接口技能,适宜影像传输的专用型数字化接口,可同时传送音频和影像。

一、接口构造

1.1 M-PHY 接口

M-PHY分为低速模式和高速模式两种,它们的差分阻抗为100欧,采取8b/10b编码。

M-PHY分为TYPE I和TYPE II。

TYPE I不哀求参考时钟,可以利用PWM的共享时钟而TYPE II哀求利用参考时钟。

M-PHY根据速率又分为LS(Low Speed低速)和HS(High Speed高速)两大类,在HS时,TYPE I和TYPE II的信令机制是一样的;但在LS时,TYPE I利用PWM,而HS利用单独的共享参考时钟。TYPE I和TYPE II的差异见下表1.1。TYPE I利用PWM(脉冲宽度调制)调制,而TYPE II利用NRZ(non-return to zero 非归零码)编码。

表1.1 MIPI M-PHY Type-I和Type-II的差异

HS分为G1、G2、G3及G4等4个等级,而每一个Gear又分为Rate A和Rate B两个等级.如下表所示。

M-PHY HS模式传输速率表:

High speed Gear Rate A(Mbps) Rate B(Mbps)

HS_Gear 1 1248 1485

HS_Gear 2 2496 2915

HS_Gear 3 4992 5830

HS_Gear 4 9984 11661

LP(low power低功耗)分为8个等级,M-PHY LP模式传输速率如下表:

LP_Gear Data rate(Gbps)

0 0.01~3

1 3~9

2 6~18

3 12~36

4 24~72

5 48~144

6 96~288

7 192~576

时钟弹性机制:M-PHY既可以事情在Mesochronous时钟模式,也可事情在Plesiochronous时钟模式.须要把稳的是,Plesiochronous模式仅支持TYPE I。其参考时钟为19.2、26、38.4和52MHz等.

图1.2 MIPI M-PHY Type-1和 Type-II接口模式比拟

能耗比较:

图1.3 MIPI M-PHY状态能耗比较

图1.4 M-PHY 状态和突发传输的范例运用

1.2 D-PHY

2线差分串行接口。同样也用于数码摄像头和高清显示器件,CSI作为Camera接口,DSI作为显示屏接口。 一样平常时钟差分比和数据差分对分开,如下图所示(4个数据差分对和一个时钟差分对,统共10根线)。D-PHY具有低本钱、低功耗、源同步和高速等4个特性,使其特殊适宜于移动终端设备的运用。其采取主—从构造和双向-单工构造。个中时钟旗子暗记为单向,由主至从;而数据可以是单向或双向,取决于须要传输的内容,并通过TOKEN(令牌)来决定方向(在半双工时,反向传输带宽为正向传输带宽的1/4),其速率范围是80~1000 Mbps.低功耗模式时,其最大速率为10Mbps.其编码采取8b/9b;自D-PHY V2.1 开始就可以支持每对差分线速率达4.5Gbps,统共4对差分线速率可达18Gbps。

MIPI D-PHY采取主从构造的办法,采取源同步的机制,Data相对付Clock以DDR(Double Data Rate)办法进行数据传输,保持正交相位关系以确保在吸收端可靠的建立和保持韶光裕度。常日来说数据以单一方向传输,也支持双向传输模式,比如CSI, DSI标准采取单一方向传输。D-PHY可传输的间隔最长为25~30cm或54cm/√ε(ε为介电常数)。

由于考虑到移动产品设计的功耗问题,MIPI D-PHY总线的操作模式除了正常的高速(HS, High Speed)旗子暗记传输状态之外,还定义了低速率传输--即低功耗模式(LP, Low Power)用于进行掌握指令的操作。在HS模式时旗子暗记采取差分逻辑,差分旗子暗记电压摆幅约为200mV;在LP模式时采取单端逻辑,高电平约为1.2V。其余,MIPI D-PHY也定义了一种可选的低功耗分开模式(Low Power Escape Mode),只用LP的Data旗子暗记进行数据的异步传输。

操作模式包括高速、掌握和分开模式,如下面表格描述。

D-PHY旗子暗记接口构造:

当处于HS模式时,发射端采取差分驱动模式;当不处于HS模式时,吸收端ZID端接(差分输入阻抗100 Ω)要关闭。当在吸收端Dp和Dn同时低于VTERM-EN(最大450mV)时,吸收端再打开ZID端接。如下图所示。

当处于LP模式时,发射端利用推挽式(Push-Pull)驱动办法,并且斜率可控,以降落EMI的影响;吸收端利用非端接且单真个输入电路,在每一起上侦测旗子暗记的高低状态,吸收端须要有良好的设计以规避毛刺和RF滋扰旗子暗记。 如下图所示。

从上述的HS和LP模式,发射端和吸收真个模型可以看到,首先HS差分模式下,有一定共模电压;其余,在HS和LP模式下,吸收真个端接模式分别为100 Ω和悬空。

1.3 C-PHY

C-PHY之前称为3相D-PHY,3线串行接口,发送用单端,吸收用差分,也便是一个通道Lane须要3根旗子暗记线。编码效率2.28bit/symbol,利用LP(Low Power)模式。紧张用于数码摄像头和高清显示器件。其传输数据速率可达2.5GSym/s (effective data rate of ~5.7Gbps)。一样平常情形下,Camera会用到3对通道Lane,但是也有利用到5个通道的可能性(比较前辈的手机);V2.0 C-PHY则流传宣传每对差分对可以达到6Gsps(2.28b/s),即每Lane(通道)传输速率可达13.7Gbps,9根线(三对Lane通道,每Lane通道为三根线)总速率则为41.1Gbps,

发射机采取单端逻辑,而吸收机采取差分逻辑。

二、事情事理

2.1 D-PHY接口

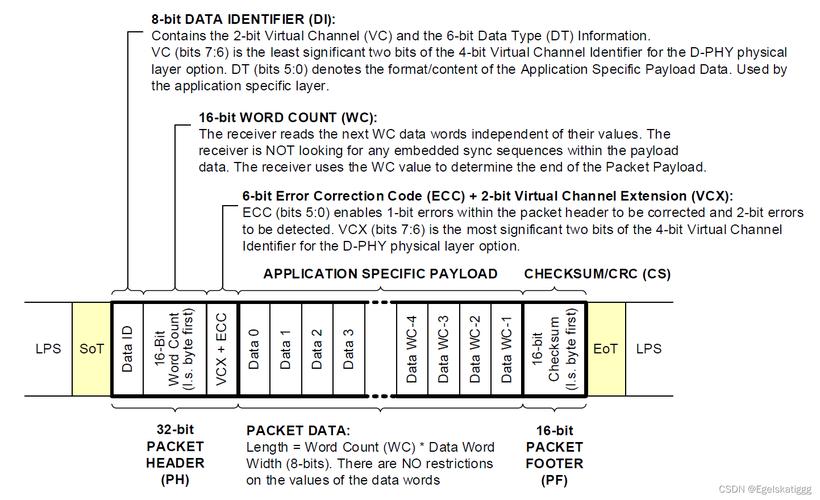

D-PHY接口包括LPS(Low Power低功耗)和HS(High Speed高速)两种速率模式。

D PHY哀求比特误码率BER<10exp(-12).一个D PHY包括一对时钟差分对和1~4个数据差分对。

一个D-PHY设备内部大致包括(如下图所示):

a High-Speed Transmitter (HS-TX)

a High-Speed Receiver (HS-RX)

a Low-Power Transmitter (LP-TX),

a Low-Power Receiver (LP-RX)

a Low-Power Contention Detector (LP-CD)

图2.3 一个D-PHY收发机的内部功能示意图

数据速率:80Mbps~1Gbps(HS模式);800Kbps~10Mbps(LP模式)

HS模式高电平范围:+150 mV~+450 mV

HS模式低电平范围:-17 mV~ 217 mV

LP模式高电平范围:800 mV ~ 3.3V

LP模式低电平范围:–100 mV~ +100 mV

2.2 M-PHY

M-PHY利用差分对传输数据,其编码格式为8B/10B。它也包括高速、低速和低功耗等模式,同D-PHY一样。差分阻抗为100 OHM。

三、运用设计

对付我们而言,MIPI接口最常用的便是DSI-2(Display Serial Interface)和CSI-2(C -amera Serial Interface),当然也可能会用到DigRF.下面就先容一下DSI和CSI的运用设计。

CSI-2(当前版本为v3.0-Sep,2019)估量2020年Q1会推出v4.0.它可以支持1080P、4K、8K乃至更高分辨率的视频或图像。CSI已经被淘汰,而CSI-3则运用在M-PHY物理层上。

DSI-2 (当前V1.1),最长传输间隔可达18英寸(约为1825mm=450mm).传输层基于VESA VDC-M and VESA DSC标准,须要MIPI DCS(Display Command Set)合营利用。

DSI和DSI-2最大的差异是DSI-2可以利用C-PHY,而DSI弗成,只能利用D-PHY。

基于实际的须要,连接两个D-PHY设备之间一样平常采取微带线Micro-Stripline或带状线Stripline . D-PHY采取1对源同步的差分时钟和1~4对差分数据线来进行数据传输。数据传输采取DDR办法,即在时钟的高下边沿都有数据传输。D-PHY的物理层支持HS(High Speed)和LP(Low Power)两种事情模式。HS模式下采取低压差分旗子暗记,功耗较大,但是可以传输很高的数据速率(数据速率为80M~1Gbps); LP模式下采取单端旗子暗记,数据速率很低(<10Mbps),但是相应的功耗也很低。两种模式的结合担保了MIPI总线在须要传输大量数据(如图像)时可以高速传输,而在不须要大数据量传输时又能够减少功耗。

这里紧张先容PCB LAYOUT把稳事变如下:

差分对内的两根线间隔至少保持2倍PCB板材厚度。差分对之间要用地或电源进行隔离处理以减少耦合。参考地与旗子暗记线之间尽可能靠近。两个D-PHY设备之间的互连之直流电阻应小于5 OHM,而接地电阻要小于0.2 OHM。DSI接口发送机与吸收机之间的接口示意图。图中,Host Device主机作为DSI发送机可以是高HS发送机、LP发送机和LP吸收机,Peripheral外设作为DSI吸收机,可以是HS吸收机、LP吸收机和/或LP发送机(仅双向传输时有效)。它们有1对时钟差分比以及1~4对数据差分对。DSI接口支持Command模式和Video模式两种。

CSI接口发送机与吸收机之间的接口示意图。图中,Camera作为CSI发送机和一个CCI(Camera Control Interface)接口的从机,基带或运用场置器作为CSI吸收机和一个CCI接口的主机。它们有一对CCI(兼容于I2C接口)接口和1对时钟差分比以及1~4对数据差分对。

四、测试验证

4.1 MIPI D-PHY的旗子暗记质量测试

MIPI D-PHY的旗子暗记质量的测试方法紧张参考MIPI协会发布的CTS (D-PHY Physical Layer Conformance Test Suite)。

D-PHY物理层旗子暗记质量测试包括吸收器S参数符合性测试、吸收器物理层符合性测试和发射器物理层符合性测试三大类。

要进行MIPI旗子暗记质量的测试,首先要选择得当带宽的示波器,按照MIPI协会的哀求,测试MIPI的旗子暗记质量至少须要4GHz带宽的示波器。为了提高测试的效率,测试中推举采取4支探头分别连接clk+/clk-和data+/data-旗子暗记进行测试,对付有多条Lane的情形可以每条Lane分别测试。对付MIPI模组或芯片的测试可以根据MIPI协会推举的方法设计评估板TVB(Test Vehicle Board)并结合协会供应的RTB(Reference Termination Board)进行旗子暗记测试。

MIPI的测试包括HS旗子暗记(Data, Clock)的电气特性丈量,LP旗子暗记(Data, Clock)的电气特性,Data全局操作(Global Operation,可以理解为模式转换),Clock全局操作,HS模式下Data和Clock的时序丈量等等。

Keysight推举的MIPI D-PHY旗子暗记质量测试推举的测试配置如下:

² 宽带示波器:DSO9404A

² MIPI D-PHY旗子暗记质量测试软件:U7238A旗子暗记同等性测试选件

² 繁芜旗子暗记分离软件:N5415B InfiniiScan选件

² MIPI D-PHY 协议触发和解码软件:N8802A CSI/DSI解码选件

² 有源探头放大器:1132A×4

² 探头放大器前端附件:E2669A×4

归纳成两大类:电气特性丈量和时序丈量

u 电气参数丈量

电气参数紧张包括差分/共模电压,边沿韶光等参数丈量,关于这些参数,MIPI规范里有专门的定义。

共模电压VCMTX:丈量DP和DN之间的共模电压,这个电压常日为200mV,极限范围该当在150mV和250mV之间;

共模失落配VCMTX(1,0):丈量在差分1状态和差分0状态下,共模电压的差异。

为了降落EMI的影响,MIPI规范对这些参数有明确的哀求。而且为了降落MIPI旗子暗记对付手机里的射频旗子暗记的影响,MIPI规范也明确了在450MHz以上共模颠簸电压必须要小于15mVrms ;在50MHz到450MHz之间共模颠簸电压必须小于25mVrms。

测试时,示波器同等性测试软件必须通过加入巴特沃兹IIR高通和带通滤波器来完成这两个参数的丈量。MIPI 的HS旗子暗记旗子暗记摆幅本身就很小在200mV,共模噪声也就在25毫伏以下,以是哀求丈量示波器的本底噪声也尽可能的小,这样才能担保丈量结果的信噪比更高或者说提高丈量结果的裕度。

对付从事MIPI CSI/DSI的芯片和外围模块开拓的用户来说,须要的是能够全面地验证被测件的功能及在各种可能涌现的情形下的表现,这仅仅依赖示波器里供应的旗子暗记质量剖析和协议解码功能就不太够,此时就须要全套的MIPI CSI/DSI 的协议剖析和旗子暗记勉励方案(Keysight供应):

² 16800/16900系列逻辑剖析仪:天生繁芜的CSI/DSI的数据包,并对捕获到的数据包进行解包剖析;

² N4861B MIPI CSI/DSI数据勉励模块:把逻辑剖析仪产生的数据包按CSI/DSI的旗子暗记格式和电平送给被测件;

² N4851B MIPI CSI/DSI协议剖析模块:用于捕获实际CSI/DSI数据线上的旗子暗记并送给逻辑剖析仪进行数据解析。

下面两图分别为显示屏DSI总路线测试和摄像头CSI总线测试的示意图。

CLK的模式转换时序

Data的模式转换时序参数波形图

Data和CLK的时序关系:Data以源同步的机制进行旗子暗记传输,在发射端Data和CLK有一定skew(斜率)的哀求,吸收端Data和CLK要有一定的建立保持韶光的哀求,详见下表哀求。

示波器软件通过CLK和Data重修Data眼图,通过直方统计图丈量旁边两个交叉点的分布,从而丈量出来Data和Clock的skew,这种统计的方法可以找到最差的结果,可以担保丈量结果的可靠性。

丈量MIPI的探头探测方法

MIPI D-PHY有LP和HS两种状态,LP的旗子暗记为单端模式,HS为差分模式,其余在规范里规定了HS旗子暗记的共模参数的指标以及不同频率范围内共模电压的颠簸值,以及模式转换的丈量,以是从探头上要采取单端探头丈量CLK+ / CLK-,以及Data + / Data -.

规范推举利用4个探头,分别探测Data Lane +/-, CLK +/-,这样可以利用同等性测试软件一次性完全测试,但为了节约本钱,也可以选用3个探头探测,在丈量Data HS模式旗子暗记的参数及时序干系参数时,CLK可以利用差分探头测试,DP/DN利用两个单端探头分别测试,丈量CLK的模式转换也须要3个探头,须要调换连接CLK +/-分别探测,再连接一个Data旗子暗记。详细的连接办法,U7238A测试软件会给出完全的图示连接指南,按照推举的探测办法探测。

测试夹具端接和非端接

根据前面所说,MIPI分为HS和LP两种模式,由于端接办法的差异,以是在测试时也要考虑到这些问题,丈量HS旗子暗记要端接100欧姆,LP旗子暗记是没有端接丈量。分两种情形

1. 如果用户是做处理器芯片或摄像头芯片模组测试发射端旗子暗记的性能,须要准备两种测试夹具在两种模式下切换端接。

2. 如果用户做的系统级测试,由于测试环境里吸收端包括端接电路,以是不用特殊去考虑端接,利用探头焊接在电路上进行旗子暗记的丈量。

对付端接夹具MIPI官方有专门的参考端接板如下图所示,用户也可以自己制作端接夹具(100欧姆端接及无端接两种接口,以及丈量LP旗子暗记斜率及边沿韶光是哀求的load)利用手动办法进行测试,如果是这种夹具可以考虑在板上做标准的2.54mm插座或SMA接口,用Keysight E2678A或者N5380A探头前端进行测试。

4.2 MIPI M-PHY的旗子暗记质量测试

MIPI M-PHY在HS测试内容上 有一些比较大的更新,比如说要包括眼图的丈量,Tj和Dj的丈量,共模功率谱丈量等等。以下是按照M-PHY的测试规范哀求的一些测试项目:

• Test 1.1.1 – HS-TX Differential DC Output Voltage Amplitude (VDIF-DC-xA-xT-TX)

• Test 1.1.2 – HS-TX Transmitter Eye Opening(TEYE-TX)

• Test 1.1.3 – HS-TX Maximum Differential AC Output Voltage Amplitude (VDIF-AC-xA-xT-TX)

• Test 1.1.4 – HS-TX Common Mode Output Voltage Amplitude (VCM-xA-TX)

• Test 1.1.6 – HS-TX Lane-to-Lane Skew (TL2L-SKEW-HS-TX)

• Test 1.1.7 – HS-TX Slew Rate (SRDIF-TX)

• Test 1.1.10 – HS-TX Intra-Lane Output Skew (TINTRA-SKEW-TX)

• Test 1.1.11 – HS-TX Transmitter Pulse Width (TPULSE-TX)

• Test 1.1.12 – HS-TX Total Jitter (TJTX)

• Test 1.1.13 – HS-TX Deterministic Jitter (DJTX)

• Test 1.1.14 – HS-TX Short-Term Total Jitter (STTJTX)

• Test 1.1.15 – HS-TX Short-Term Deterministic Jitter (STDJTX)

• Test 1.1.17 – HS-TX Transmitter Frequency Offset (fOFFSET-TX)

从测试的内容来看很靠近传统的高速串行旗子暗记的测试方法,规范里也定义了同等性测试码型CRPAT(同等性随机码型)和CJPAT(同等性抖动测试码型),前者紧张针对发射旗子暗记的抖动等参数丈量,后者紧张为了验证吸收真个PLL或者时钟规复的加压测试。

关于MIPI接口物理层参数的测试与验证,MIPI同盟制订了专门的CTS(Conformance Test Suite),参考相应的CTS就可以完成物理层符合性的测试。

MIPI M-PHY CTS rev. 1.0

作为MIPI组织授权的认证测试机构UNH-IOL,卖力开拓MIPI测试方法和发布同等性测试规范,对MIPI产品进行规范的认证测试,从他们官方供应的测试报告实例来看,可以明确看到他们MIPI D-PHY的测试采取的是安捷伦的示波器,可以从下面的链接下载干系的测试规范及测试实例。 https://www.iol.unh.edu/services/testing/mipi/testsuites.php

测试示波器的哀求:

为了担保MIPI旗子暗记的能够准确丈量: MIPI D-PHY同等性测试规范标准(V1.0)哀求示波器带宽至少为4G; MIPI M-PHY的同等性测试规范(V 0.84),对付G1/G2/G3的标准哀求带宽至少为5GHz /10GHz /20GHz,这个带宽标准如何而来的呢,我们以Gear 3的5.8304Gbps为例: UI (unit interval 位宽) = 1/5.8304G = 171.5ps

根据规范里的哀求,20%~80%上升/低落韶光最小为10% UI,推算最小上升/低落韶光为17.15ps,那么示波器为了准确丈量边沿韶光须要的带宽(10%丈量偏差) BWscope = 0.4/17.15 ps = 23.3 GHz,如果哀求3%的丈量偏差,须要的带宽要更高。

一个完全的测试DSI和CSI的示意图如下所示。